# Analysis & Design of Two-Stage Operational

# **Trans-conductance** Amplifier

A

Thesis

Submitted towards the Requirement for the Award of degree of **DOCTOR OF PHILOSOPHY**

IN

**Electronics and Communication Engineering** Under the faculty of Engineering & Technology

By

Shikha Goswami (Enrollment No 161510506243) Under the Supervision of Dr. Satnam Singh **H.O.D** Department of Electronics & Communication Engineering P.K UNIVERSITY, SHIVPURI (M.P.)

YEAR - 2023

P.K. UNIVERSITY, SHIVPURI (M.P.) - 473665

i

| CERTIFICATE OF COPYRIGHT   | п         |

|----------------------------|-----------|

| CANDIDATE DECLARATION      | ш         |

| ACKNOWLEDGEMENT            |           |

| DEDICATION                 | IV        |

| CERTIFICATE OF SUPERVISIOR | V         |

| SUMMARY                    | VI        |

| INDEX                      | VII-XIII  |

| LIST OF FIGURE             | XIII-XVII |

| LIST OF TABLES             | XVIII-XXI |

| ABBREVIATIONS              | XXII-XXIV |

|                            | XXV       |

# CERTIFICATE OF COPYRIGHT

This work is done by me in Original, the result and all data are produce by me is totally obtained by me.

Shikha Goswami

ii

# **P K UNIVERSITY**

# University Established under Section 2f of UGC act 1956 vide mp government act no 17 of 2015

# Village Thanra, Karera NH 27, district Shivpuri (M.P)

# **CANDIDATE DECLARATION**

It hereby declare that the thesis entitled "Analysis & Design of two-stage Operational Trans-conductance Amplifier" is my own work conducted under the supervision of Dr. Satnam Singh approved by the research degree Committee of the University and that I have put in more than 200 days\ 600 hrs of attendance with the supervisor.

I further declare that to the best of my knowledge this thesis does not contain any part of any work which has been submitted for the award of any degree either by this University or by any other University/ deemed University without a proper citation.

(Signature of the Candidate) Enrollment Number: 161510506243 Registration Number:

# ACKNOWLEGEMENT

At the onset of the acknowledgement, I ascribe all glory to the Gracious "GOD" from whom all good things come, who has showered his choicest blessings and benevolent graces up on me in life and bestowing me with the blessing to see this day.

With a sense of profound ecstasy and reverence, I do express my gratitude to honorable Chancellor Mr. J.P Sharma sir P.K University, Shivpuri (M.P) for their benevolent cooperation, valuable advices and providing encouragement during the tenure of the thesis work.

I am very much thankful to our honorable vice Chancellor **Dr. Ranjeet Singh** P.K University, Shivpuri (M.P) sir for providing us with best facilities in the department

I remain deeply indebted to honorable **Mr. Jitendra Mishra**, Director, P.k University, for his help and encouragement during the course of investigation.

Mere words can never suffice to express the sense of my ineptness and heartfelt adoration to my honorable Chairman of Advisory Committee **Dr. Satnam Singh** Head of the Department Electronics and Communication Engineering, P.K. University Shivpuri (M.P) for his invaluable and ceaseless guidance, precious counsel, unstinted help, constant encouragement during the course of investigation and constructive criticism in the preparation of the manuscript of the thesis which can never be forgotten. His valuable suggestions, innovative ideas and meticulous nature helped me in the execution of my investigation and degree. His close monitoring and stimulating influence made the work complete with perfection.

I do express my sincere thanks to Academics Dean **Dr. Pawan Kumar** also I thanks to Incharge Research Cell **Dr. Bhaskar Nalla** for their value suggestions & Faculty of Engineering & Technology, P.K University for providing all sorts of facilities to conduct the course and research activities.

My sincere thanks to **Dr. Deepesh Namdev Registrar, P.K University** for his valuable suggestions and his innovative ideas. I am also thankful to all the non-teaching Staff of the Department of Electronics & Communication Engineering and Dean, Post Graduate Studies and Dean, Faculty of Engineering & Technology, P.K University, for their innovative suggestions, help and encouragement throughout the thesis work.

v

I express my sincere thanks to my teaching and non-teaching Staff, Department of Electronics & Communication Engineering, ITM University, Gwalior who all along helped me and guided me until this work is done. "Your commitment and cool composure towards me shall never fade from my memories". I do express my sincere thanks to the teaching and non-teaching Staff of Faculty of Engineering Shri Rawatpura Sarkar Group of Institutions Datia (M.P) for their constant help, support and inspirations in times of need.

I shall be failing in my duty if I don't express my obligation to teaching Staff Holy Cross Ashram School Datia (M.P). I am also thankful to all wishers, who's direct and indirect blessing help me to continue my study.

In thanking all these people, I have no words to express my special thanks to all my seniors for their constant help, support and inspirations in times of need

I must emphasize that I am fully responsible for any short coming that remains. I have special thanks to all my loving friends Nitya, Nisha, versha, ruchi anamika ,sadhna , atibhi, raghav for their help and constant enlivening company and good wishes that greatly expedited my thesis work and the course of the study.

I express my heartiness thanks to my loving juniors **Meenakshi and Gajendra patel**, for their help and constant enlivening company and good wishes that greatly expedited my thesis work and the course of the study.

Words and deeds are really insufficient to repay the unending love, constant inspiration and cooperation from all of my Well Wishers.

So much deserve my thanks to my father Mr. Rakesh Goswami and mother Mrs Usha Goswami and my father in law Mr. Suryakant Rai and mother in law Mrs. Kusumlata Rai for always loving, caring and motivating to attain this height. Their pure affection, concern, inspirations and constant prayers have always been my lifeline and the joy of living. I have no greater words to say to you, to let you know how much you mean to me.

Word can never express the ineptness but I done to take this opportunity to pay my deepest sense of gratitude with profound obeisance and heartiest thanks to over my vulnerable Uncle Mr. Swadesh Goswami and Aunti Mrs Mamta Goswami also thankful to my in laws Shri Shashikant Rai, Aunti Mrs. Arundhati Rai, Mrs. Rajmuni Rai, Brothers Mr. Vishal Goswami & Vikas Goswami and my Brother in laws Er. Prashant Rai, Sahil Rai, Sisters

Anamika sharma & Ruchi sharma and also my sisters in laws Renu Rai, Romi Rai, Soni Rai, Rani Rai, Dolly Rai, Sibbu Rai for their unfailing love, good working, constant pursuing untiring support and encouragement brought out to me in my life and whose blessing and inspirations silently work in bringing me up near to my long cherished aspiration.

I would like to express my sincere thanks to my administrative guide Prof. Anand K. Tripathi, P.K University, Shivpuri (M.P) & Dr Zakir Ali, Assistant Professor and Head of E.C Engineering Deparment, BIET, Jhansi (U.P.) for their supervision, support, patience and guidance for correcting my mistakes and giving constructive criticism so that I can improve for better.

Finally, I have to thank my son Vedant & Husband love of my life, Dr. Shushant, for keeping things going and for always showing how proud they are of me.

The last word goes for Raghav Radhya & Shivi, my nephew & niece have also been generous with their love and encouragement despite the long distance between us and who has given me the extra strength and motivation to get things done.

Dated: 19 June, 2023

SWERP

(Shikha goswami) Place: Shivpuri, (M.P.)

# CHAPTER 1 INTRODUCTION

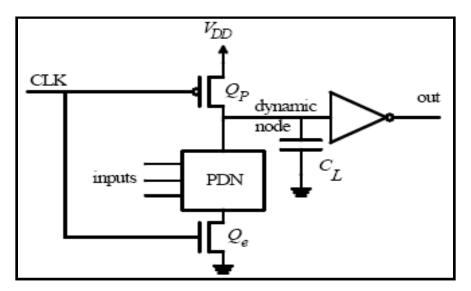

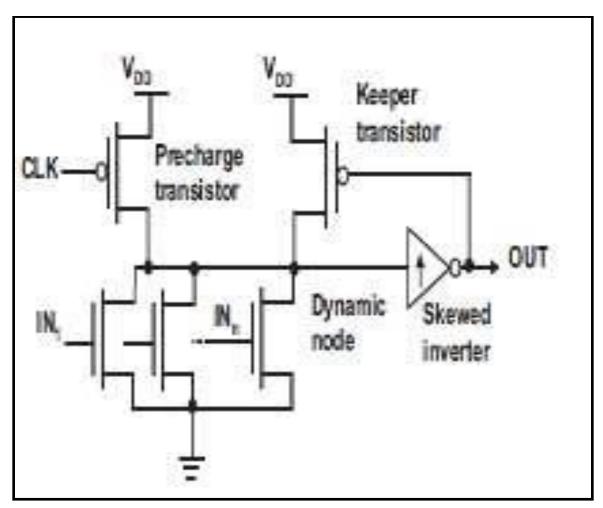

The operational trans-conductance amplifier (OTA) is an amplifier which has differential input voltage for generating an output current. Hence OTA is control current source (VCCS). Also there is generally an additional input for a current to control the amplifier's therefore, the OTA is same as standard operational amplifier in that it has a high impedance differential input stage and that is to be used with negative feedback. Because of development in VLSI technology the size of CMOS decreases and power supply also decreases. Thus the OTA is a basic binding block in many of analog circuits with linear input and output characteristics also OP-AMP is widely used in analog circuit include such as neural networks and Instrumentation amplifier with ADC and Filter circuit. The operational Trans-conductance Amplifier (OTA) is basically same as that of conventional operational Amplifiers in which both having Differential inputs also the basic difference between OTA and conventional operational Amplifier is that in OTA the output is in form of current but in conventional Op-Amps output is in form of Voltage. The Operational trans-conductance amplifier is popular for implementing voltage controlled oscillators (VCO) and filters (VCF) for analog music synthesizers and neural networks also instrumentation amplifier because it can be also like two-quadrant multiplier. Fast and high gain operationaltrans-conductance amplifiers (OTAs) are an integral part of switched capacitor circuits. The basic application for trans-conductance is to drive low-impedance sinks such as coaxial cable with less distortion at high bandwidth. The operational trans-conductance has been traditionally implemented using a cascade of two stages to provide a high gain. Also through, the lower supply results in lower power consumption, as the supply currents. Modifying and checking the settling performance by Phase-margin adjustments has been proposed in the literature. However, also for two-stage amplifiers, better phase margin does not always imply faster settling. A transconductance is a voltage controlled current source and also more specifically the term operational comes from the fact that it takes the difference of two voltages as the input for the current conversion.

Also trans-conductance amplifiers are versatile building blocks that intrinsically offer wide bandwidth for many of types of amplifiers. The OTA, or voltage-controlled current source, can be viewed as an ideal transistor. As the transistor model, it has three terminals: a high input impedance (base, or B); a low-impedance input/output (emitter, or E); and a current output (collector, or C). However, unlike a bipolar transistor, the OTA is self-biased and has bipolar output, meaning that the output current source can either source or sink the output current. The output current is zero for a zero base-emitter voltage. AC-inputs centered on zero produce an output current that is bipolar and also centered on zero. The trans-conductance element is traditionally adjustable with an external resistance, allowing trade-offs in bandwidth, quiescent current, and gain. Used as a basic building block, an OTA element simplifies designs of automatic gain control (AGC) amplifiers, light-emitting diode (LED) driver circuits, fast-pulse integrators, control loops for capacitive sensors, and active filters, as well as other applications.

Today operational amplifiers (OPAMPs) are widely used as basic building blocks in implementing a variety of analog applications from amplifiers, summers, integrators, and differentiators to more complicated applications such as filters and oscillators. Using OPAMPs greatly simplifies design, analysis, and implementation for analog applications. OPAMPs work well for low-frequency applications, such as audio and video systems. For higher frequencies, however, OPAMP designs become difficult due to their frequency limit. At those high frequencies, operational trans-conductance amplifiers (OTAs) are deemed to be promising to replace OPAMPS as the building blocks. Theories of using OTAs as the building blocks for analog applications have been well developed Meyer- et al. [1]. To date, with much effort dedicated by analog IC researchers and the continuous scaling-down on commercial semiconductor technologies, the reported OTAs can work up to several hundred MHz. In this thesis, a fully differential high frequency OTA suitable for microwave applications will be presented which has a large trans-conductance up to 10 GHz. It will also be shown that there are more applications of the OTAs other than the aforementioned analog applications that are specifically interesting at microwave frequencies. All of these developments indicate that OTA microwave circuits are just around the corner.

Moreover trans-conductance enhancers are adaptable construction hinders that inalienably offer wide bandwidth for an enormous number of kinds of intensifiers The OTA, or voltage-controlled current source, can be seen as an ideal semiconductor. As the semiconductor model, it has three terminals: a high information impedance (base, or B); a low-impedance input/yield (producer, or E); and a current yield (locater, or C). Regardless, rather than a bipolar semiconductor, the OTA

is self-uneven and has bipolar yield, suggesting that the yield current source can either source or sink the yield current. The yield current is zero for a zero base-maker voltage. AC-inputs focused on zero produce a yield current that is bipolar and moreover centered around nothing. The transconductance part is generally adaptable with an external resistance, allowing bargains in information transmission, quiet current, and gain. Used as a basic design block, an OTA segment chips away at plans of modified gain control (AGC) intensifiers, light-releasing diode (LED) driver circuits, speedy heartbeat integrators, control circles for capacitive sensors, and dynamic channels, similarly as various applications. Using OPAMPs unfathomably enhances plan, examination, and execution for straightforward applications. OPAMPs work splendidly for lowrepeat applications, similar to sound and video systems. For higher frequencies, regardless, OPAMP plans become irksome due to their repeat limit Hokari et al. [2]. At those high frequencies, operational trans-conductance speakers (OTAs) are seen as promising to supersede OPAMPS as the development blocks. Speculations of utilizing OTAs as the development blocks for clear applications have been all through made got inconvenient as a result of their repeat limit . At those high frequencies, operational trans-conductance enhancers (OTAs) are viewed as promising to replace OPAMPS as the design blocks. Theories of using OTAs as the construction blocks for straightforward applications have been especially advanced. Until this point, with much effort submitted by basic IC researchers and the steady cutting back on business semiconductor progresses, the nitty gritty OTAs can work up to a couple hundred MHz.

#### **1.1 Motivation of Research**

As we had been discussed in the preceding sections, the operational amplifier is a very important component in most analog and mixed systems. Thus it is very crucial that the requirements of matched with the current trends offered by the industry. In the conventional electronics market, low-voltage operation, along with low-power dissipation is an important parameter for all devices. Operational amplifier is no exception to this. It is important that they also evolve to be compatible in this low-voltage low-power environment. This is the motivation behind the research carried out.

A two-stage operational trans-conductance amplifier design had been proposed. To avoid the Cascading the output swing reduction that results in the case of cascading it is important because in low voltage operation the already small swing cannot be further compromised. The cascaded connection of the two stages also ensures an improvement in the gainoffered by the device.

The proposed implementation is designed to use a two stage operational trans-conductance amplifier. This increases the trans-conductance of the stage-I, thereby improving the gain offered by the stage. In addition to this, the final gain offered by the circuit has been further enhanced by making use of a gain- boosting circuit.

Therefore, the proposed design is the future of op-amp technology. It improves the gain of the device while maintaining its viability as an efficient low voltage component that can used in the present day electronics.

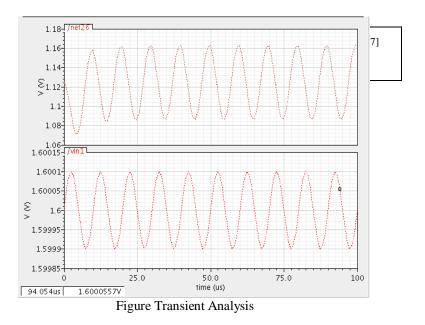

The existing design methods for two-stage OTAs often leadto sub optimal solutions because they decouple inter-related metrics like noise and settling performance. In our approach, the cadence tool is used to analysis the transient response, AC response and phase plot of the OTA and settling time has been observed on the simulation. For the optimization routine, there is no need to interface with a circuit simulator because all significant devices parasitic are included in the tool.

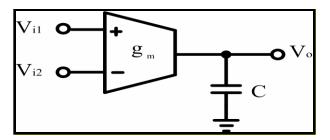

### 1.2. Operational trans-conductance Amplifier

An operational trans-conductance speaker is a current yield intensifier and a voltage input. The voltage Vin of the data and the yield current Io are related to each other by a consistent of proportionality and proportionality of predictable is the trans-conductance "gm" of the intensifier.

$$Io=gmVin \tag{1.1}$$

Where gm= Trans-conductance of OTA.

Vin= Differential info voltage

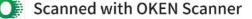

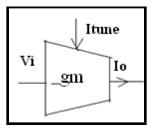

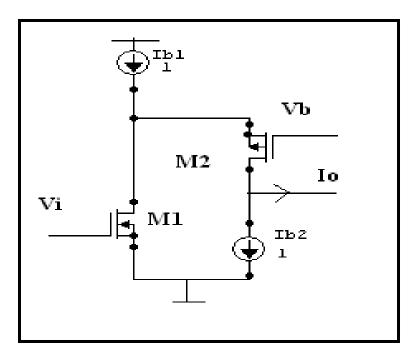

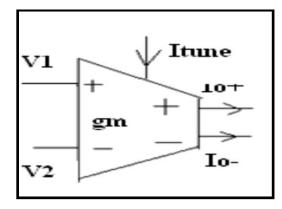

Figure 1 tells the best way to address OTA emblematically

Figure 1.2: symbol OF OTA

The trans-conductance gm of the OTA can be changed by fluctuating the estimation of the outer controlling current IC.

$$Gm = KIC \tag{1.2}$$

Where K = reasonable steady of proportionality

Subbing condition (2) into condition (1), we get,

$$IO = K Vin IC$$

(1.3)

Condition (3) uncovers to us that yield current is relating to the consequence of V<sub>in</sub>and IC.

OTA include a differential semiconductor pair with a current mirror circuit going probably as a load. Since OTA deals with the head of taking care of current rather than voltage, it is also a distinctively speedy contraption. As gm can be constrained by changing the control current IC, and the OTA are reasonable to electronically programmable capacities.

### 1.3 OTA Circuit view and its idea

#### 1.3.1 Basic Voltage Amplifiers

This part will look at a subset of general voltage enhancers, both with and without negative analysis. For extra information about the rich combination of speaker arrangements open using the OTA, the reference Sakurai T [3] is inconceivably useful. Figure 2 shows an adjusting enhancer recognized with an OTA which can give controllable increment, yet which similarly uses negative contribution to diminish the yield resistance. Actually, the yield resistance is

furthermore now controllable through the transconductance. The voltage gain and yield impedance are given by

$$\frac{v_0}{v_i} \equiv \frac{1 - g_m R_2}{1 + g_m R_1}$$

(1.4)

The derivation of Equation (4) is acquainted in a reference area with show the normal examination required while overseeing OTA-based circuits.

Conditions clearly, is nothing else than a non-revamping speaker. This isn't strange, since one of the properties of negative analysis is the practically complete dependence of the expansion on the information extent figuratively speaking.

The last outline of a key design block intensifier using OTA's is showed up in Figure 3. This is an outline of an all-OTA speaker, with the voltage gain and yield impedance.

The expansion and yield impedance are absolutely settable by the external streams, with no external, standoffish sections beside those normal to create the current from a standard voltage source.

1.3.2. Dynamic Filters with the OTA

Dynamic channels are a standard utilization of the activity amp which can benefit immensely from the controllability of the OTA Hiser at.el [4]. The straightforward speculation and the circuit schematics for the fundamental unique channels using activity amps are presented in an impressive parcel of the course books being utilized in Electronics Technology or Engineering programs. What makes the OTA so engaging in these circuits is the ability to shape channel circuits with voltage-variable control (through the IABC commitment) over different key execution limits of the channel. The controlled limit can be the mid band gain of the circuit, as adequately recognized in the direct circuits in the past territory Wang at el. [5]. Then again, OTA-based unique channels can use the external tendency setting to control the space of the fundamental repeat, or 3-dB repeat, in a channel. The accompanying shrewd development in controllability is the plan with the expectation of complimentary increment and essential repeat setting. Different other unique channels can be recognized with the OTA. These enable to not simply change the fundamental repeat, the increment, or both, yet notwithstanding secure the

condition of the response. For instance, one should control the essential repeat of the channel, anyway without changing the pass ban d wave. It is even possible to change the sort of response from low pass to all pass to high pass by consistent difference in the trans-conductance gm.

A very essential delineation of a first-demand (one shaft contrasting with a move off speed of - 20 dB/decade in repeat) low pass direct is showed up in. The voltage obtain over the whole repeat range, and the - 3 dB repeat, is given by

#### 1.3.3. Some Non-ideal Features of the OTA

Maybe the best disadvantage of the principle transformations of the OTA was the confined extent of the information differential voltage swing. This declaration ought to be qualified in any occasion two distinct ways. In any case, the confined information voltage swings applies just if the OTA is being used in the open-circle plan. In light of everything, if the qualification mode voltage outperforms around 25 mV, and the load resistance is for the most part low (with the objective that the open-circle obtain is pretty much nothing), by then the circuit is finished working in the immediate territory. This results in the yield signal being deformed because of a nonlinear voltage move work. Clearly, for circuits which use negative analysis, i.e., are worked in shut circle conditions, by then direct lead is kept up.

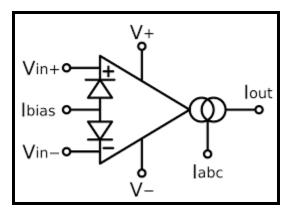

The ensuing passing remark is that the later types of the OTA, for instance, the Harris CA3280A, National Semiconductor's LM13600, and Philips' NE5517, all usage inside linearizing diodes at the information differential pair of the OTA. These make the OTA's yield current a straight limit of the intensifier inclination current over a wide extent of differential data voltages. Figure 6 shows an ordinary biasing plan for a nonexclusive business OTA. The control voltage, VCTL, is used to make the speaker tendency current, IABC, through the resistor RABC. The linearizing diodes, which are combined on-chip in the business OTA's referred to above, can be uneven on through the positive power supply voltage, +VCC. The examination of the linearization circuit

and its effect on the and in a couple of the huge vendors Sakurai at

yield current can be found in application notes from the el. [6]

#### Figure 1.3.3 (a) circuit produces a yield current

OTAs circuits are what produce a yield current as a reaction to a differential voltage input. Its conduct ideal is portrayed by an impedance of high info stage and impedance of high yield stage, as demonstrated in Fig. less impedance (even in open circle circuits) and the possibility of achieving very low trans-conductance Schmitz et al. [7]. The trans-conductance reaction of the differential info pair is anything but a straight capacity of its differential information voltage Linares at el. [8]. This is brought about by the conditions that portray the MOS semiconductors and their area of activity Snelgrove et.al [9]. Since fragile inversion territory is overpowered by emotional associations and strong inversion area by square-law conditions, moderate inversion locale is generally proposed in OTA plan since it offers the best tradeoff between the arrangement limits, as shown by Bisdounis.L, et.al [10]. To expand linearity, a few upgrades should be possible to the differential pair Dutta.S, et al. (see [11]–[13]). From the recorded more than, an adjusted variation of the Krummenacher plan Shivaling.S et al [11] and executed in Johnson R.A et al. [14] was used in the OTA planned for the improvement gadget.

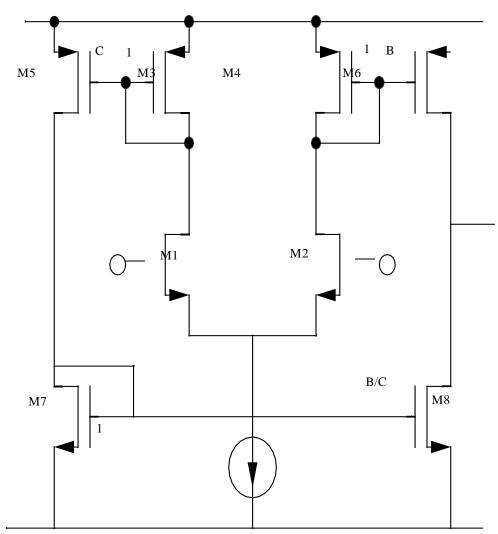

The yield stage uses current mirrors to add both I+ and I- streams to get Iout. Silveira.F at el. [15] shows that using successive equivalent current mirrors grants scaling the trans-conductance in to substantially more humble characteristics without impacting its immediate reach. For the current case, this procedure is utilized to acquire one fourth of the ordinary. Rofougaran.A, at el. [16] The full circuit arranged is showed up in Fig. 3, in which semiconductors named as M1, M3 and M5 are formed by an assortment of three courses of action related unitary semiconductors while M2-named semiconductors use a semiconductor display in plan relationship too. This is made to diminish the sidelong scattering impacts and mitigate fumble surrenders that would show if greater semiconductors are used as opposed to semiconductors are known as the symmetric diffusor, which are trustworthy of improving the straight response of the yield current; M3 semiconductors are utilized to duplicate one of the current branches into the opposite side to get a solitary finished gadget. The yield trans-conductance ttm can be drawn nearer by the accompanying condition:

Where m tends to the scale factor due to the lower current mirror, gm1 and gm2 address the trans-conductance of M1 furthermore, M2 semiconductors, separately. Various conditions consistently drew in with hand-check MOS basic arrangement is showed up in the going with set. Kuhn.W, at el [18].These conditions are gotten from the EKV model and they apply for all regions of action of the semiconductors

Where Ibi tends to the DC inclination current showed up in figure Izi is the normalization current, µCox and n are development fabricate limits, W/L tends to the semiconductor estimations and  $\varphi$ t is the warm voltage. From the past conditions, it very well may be seen that when the architect requires satisfying certain plan goals, numerous boundaries are associated with the plan cycle. The typical plan system is situated in fixing a few estimations of the circuit (generally a portion of the semiconductor measurements) and changes different boundaries to satisfy the necessities. Regardless, this cycle can take a couple of steps of experimentation tests. OTAs are particularly portrayed by its straight scope of trans-conductance, characterized as the scope of differential information voltage that creates a consistent trans-conductance esteem. Since OTAs are not totally straight circuits, the trans-conductance response may change according to its arrangement and movement plans. Because of this, the creator needs to characterize the accuracy of the straight in view of the ideal changeability, twisting or deviation of the circuit reaction. The last idea can't immediate the significance of general conditions to show the straight reach. A few approximations are characterized terms, most reenactments and investigations executed show that the straight reach V is straightforwardly reliant of the DC inclination current and the elements of semiconductors M1 and M2:

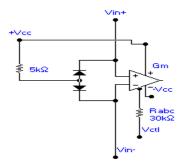

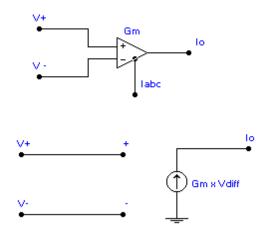

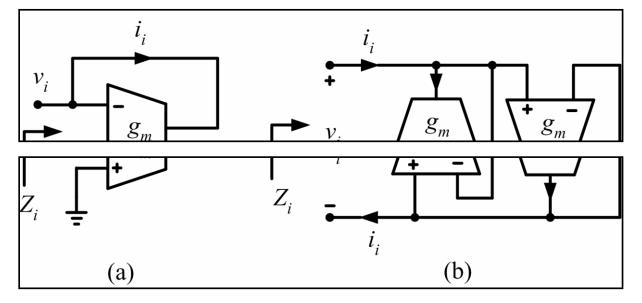

To improve a structure it is essential to separate it completely. We present a clear depiction of the plan of OTA and the diverse depiction limits this is the initial move towards detailing the model for data limit with regards to a specific framework. The schematic image and identical circuit model for an operational trans-conductance enhancer are appeared in Figure 1.3.

Fig 1.3.3(b): OTA Symbol and Equivalent Circuit

The OTA changes a differential as the info voltage over to a yield current relative addition boundary to a trans-conductance Gm=io/vi. Ideally, the information and yield securities are boundless (Ri =Ro= $\infty$ ) so much that ii=iRo=0 and the yield current is held solely by the load. The conventional OTA is designated A class intensifier and is fit for delivering max of inclination current applied yield streams equivalent. The same circuit model demonstrates that the trans-conductance enhancer creates a current (io) yield relatively to an information voltage (vi) in view of the trans-conductance acquire. Furthermore the normal OTA is isolated from various speakers by the way that its single high impedance center point is arranged at the yield terminal. The trans-conductance which doesn't utilize a yield cushion and is consequently, just fit for driving burdens capacitive

Likewise we can say an operational ideal trans-conductance intensifier (OTA) is a voltagecontrolled current medium, with a steady trans-conductance and endless information and yield impedances, as outlined in figure it tends to be portrayed by the articulations, Where VO and IO characterize the information voltage and the yield current individually, and gm is transconductance with a consistent worth ideal. Zi and ZO in address the info and yield impedances separately. For general reasons for existing, are precisely to assess an OTA's exhibition? For the most part, they become erroneous when a commonsense OTA at high recurrence or with huge information signal is concerned. Dynamic gadget nonlinearity Effects of high recurrence parasitic must be considered in such cases. Linearity and high-recurrence issues of OTAs will be tended to in the sections.

### **1.4 OTA Operation**

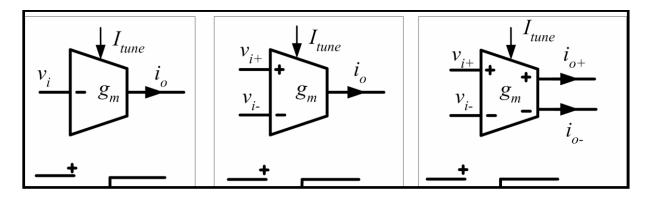

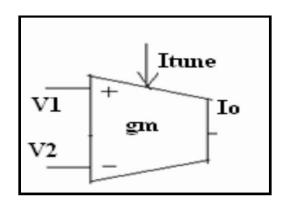

The info and yield setups are reliant, OTAs can be classified into three sorts: single information/yield, differential-input single-yield and differential info/yield. The other conceivable sort, single-input differential-yield, isn't reasonable and has not been utilized in applications which are recently depicted. The over three sorts of OTAs and their identical circuit models are introduced in Figure 1.4 According to their various setups, can be changed to communicate the three kinds of OTAs individually:

Figure 1.4 (a): three sorts of OTAs and their comparable circuit models

In OTAs, which are describes as three sorts the trans-conductance gm can be tuned through their current tendency Itune. The single information/yield trans-conductor is as depicted in figure (a) is the most straightforward to execute as a solitary NMOS basic source trans-conductor. The most simplest technique for this sort of enhancer is it makes intriguing for high repeat execution, most past works supported the while differential arrangements in Figure (b) and Fig (c) because of their versatility to associate with input courses of action and fundamental mode excusal. Two sorts' depicted in figure which have just about a comparable execution and can be replaced by each other in numerous circuits using OTAs. Li-pen et al[16] . Further the executions of three kinds of OTA will be additionally talked about.

### 1.4.1 DC Operation

The OTA is a trans-conductance type gadget, which deduces that the information voltage controls a yield current by procedures for the gadget trans conductance, named gm. This makes the OTA a voltage-controlled current source (VCCS), which is rather than the standard activity amp, which is a voltage-controlled voltage source (VCVS). What is huge and important about

the OTA's trans conductance limit is that it is obliged by an external current, the enhancer inclination current, IABC, so one gets

From this distantly controlled trans conductance, the yield current as a segment of the applied voltage contrast between the two data pins, stamped v+ and v-, is given by

Clearly, a yield voltage can be gotten from this current by fundamentally driving a resistive weight. A similar circuit for the OTA is showed up in Figure 1.4.1

Fig. 1.4.1 smaller circuit of OTA

Now, two key contrasts between the OTA and the regular operation amp should be remembered. Most importantly, since the OTA is a current source, the yield impedance of the contraption is high, rather than the activity amp's amazingly low yield impedance. Since a low yield impedance is routinely an enchanting trademark all things considered intensifiers used to drive resistive loads, sure of the more current business OTA's, like National Semiconductor's LM13600, have on-chip controlled impedance cushions. Second, it is possible to configuration circuits using the OTA that don't use negative information. Thusly, as opposed to using analysis to diminish the affectability of a circuit's presentation to device limits, the trans conductance is treated as an arrangement limit, much as resistors and capacitors are treated in activity amp based circuits. The biasing of the OTA's inside hardware is with the end goal that the all-out tranquil stockpile current [Soclof-91] is given by ISUPPLY = 3IABC. This appears to infer that the OTA can be utilized in micro power applications, even down to IABC = 1 m A. In any case, the setbacks in speed and bandwidth, which are controlled finally by IABC, can be outrageous at such low current levels.

#### 1.4.2 AC Analysis and Frequency Response

A huge piece of the dependence of open-and shut circle information move limit and repeat responses in the OTA resemble those in the customary activity amp. For a circuit utilizing negative data, a basic relationship between the shut circle data move limit, the intensifier tendency current, and the shut circle secure exists:

$$BW_{CL} = \left(\frac{20}{V}\right) I_{ABC} I \left[2\pi C_{NET} A_{CL}(0)\right]$$

(1.4.2)

where CNET is the measure of contraption convergence capacitances at the yield of the OTA and whatever stack capacitance is joined to the circuit: CNET = CO + CL. Condition (3) has the captivating outcome that particular kinds of dynamic associations, similar to dynamic channels, can have their essential frequencies obliged by the external current, IABC, which clearly can be along these lines compelled by an external voltage.

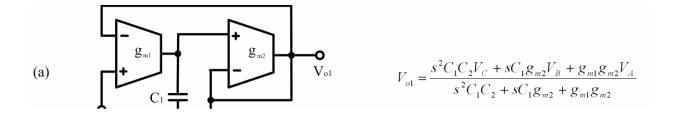

Enhancers are pervasive fundamental parts in different simple and inconsistent message inconsistent message circuits and frameworks. Operational Amplifiers are the intensifiers that have enough high forward get so when negative information; the shut circle move work is basically independent of the expansion of the activity amp [8-9]. Rule has been mishandled to make different significant direct circuits and frameworks

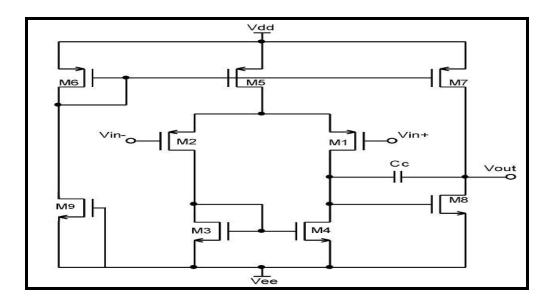

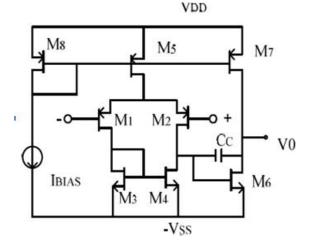

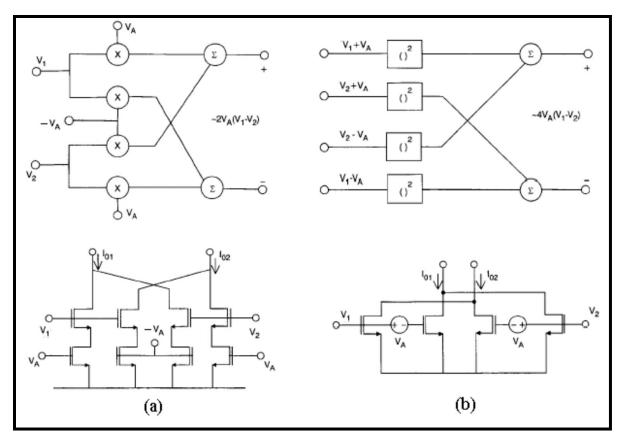

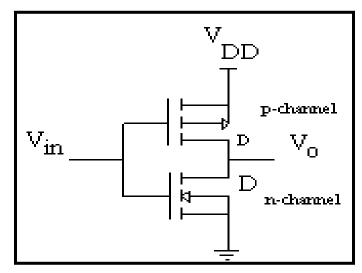

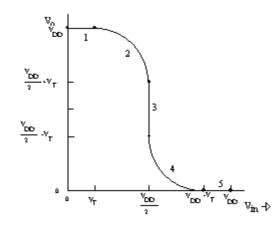

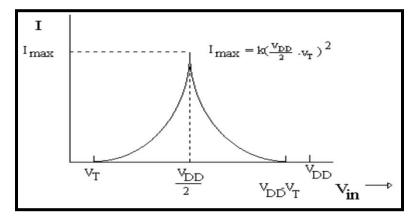

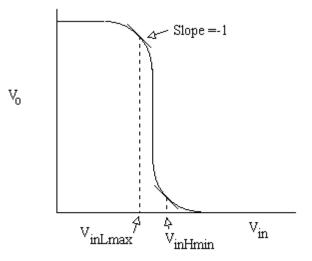

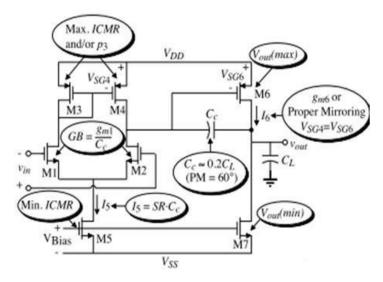

Figure 1.4.2: Two Stage Operational Amplifier

The necessity of an operation amp which is essential is to have an open circle acquire that is adequately enormous to execute the negative criticism idea. The two-period of express CMOS activity amp we consider is showed up in Figure. Accordingly the circuit includes data differential trans-conductance stage shapes the commitment of the activity amp followed by fundamental source Second stage. The typical source grows the second stage the DC procure by a huge degree and enhances the yield signal swing for a given voltage supply. This is critical in lessening the power use Kuhn et.al [18]. If the Op-Amp should drive a low resistance load the resulting stage ought to be followed by a help stage whose objective is to cut down the yield obstacle and keep a colossal sign swing.

The working point for every semiconductor predisposition circuit is given to set up in its peaceful stage. Compensation is expected to achieve stable shut circle execution Peluso at.el [20]. Nevertheless, on account of a sudden feed forward path through the Miller capacitor, a right-half-plane zero is moreover made and the stage edge is spoiled.

An especially zero, in any case, can be taken out if an authentic discrediting resistor is installed in game plan with the Miller capacitor Yue C.P et.al [23]

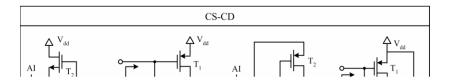

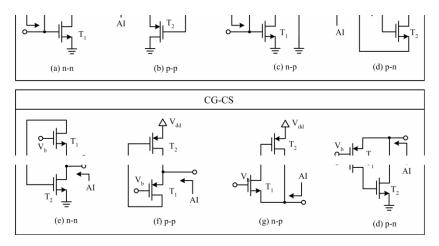

## **1.5 Different Topology of OTA**

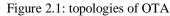

Portrayed underneath as there are five kinds of OTA geographies, every geography has its own advantages and disadvantages of each Kush Gulati et.al [26]

## 1.5.1 Single phase of OTA

OTA with single stage is as demonstrated in figure accordingly the single stage OTA is less perplexing contrast with different kinds of OTA geography as contrast with other geography its speed is higher

Figure 1.5(a): Single phase of OTA

Weakness of such an OTA is lower procured as a result of the way that it has yield impedance of this sort is respectably low course of action. At any rate this low impedance in like manner prompts high fortitude obtains move speed .

# 1.5.2 Two phase of OTA

Two stage of OTA is disadvantage of having restricted increase of the single defeat by stages OTA. In this kind of OTA arrangement two phases are utilized. Among them one of which gives high addition followed by second stage which gives high voltage swing. This modification extends the expansion up to some particular degree appeared differently in relation to single stage OTA. Regardless, this extension of extra stage in like manner fabricates multifaceted design. Moreover, the multifaceted nature extended will diminish the speed conversely with a lone period of intensifier.

Figure 1.5(b): Two phase OTA

# Benefits

- It has voltage swing as yield

- As contrast with single stage it has higher increase

# Impediments

- Compromised recurrence reaction is two phase

- Because of two phases in its plan this geography has high force utilization

- At higher frequencies it has a helpless negative Power Supply Rejection

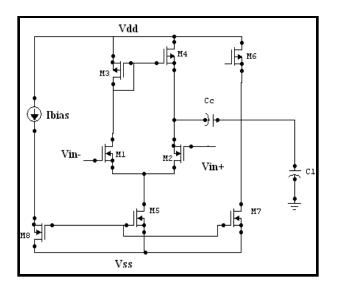

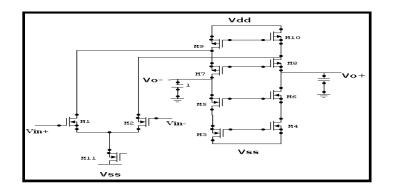

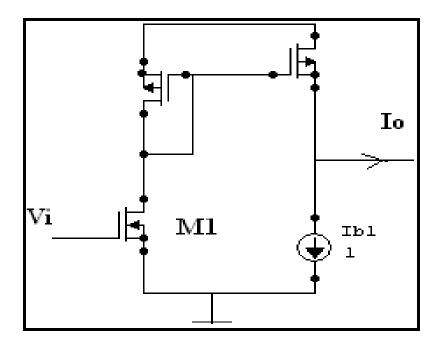

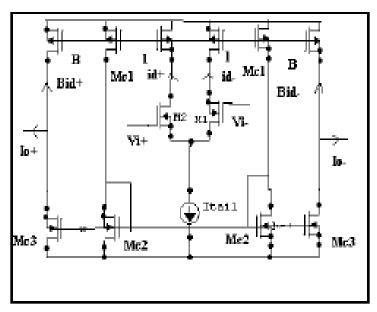

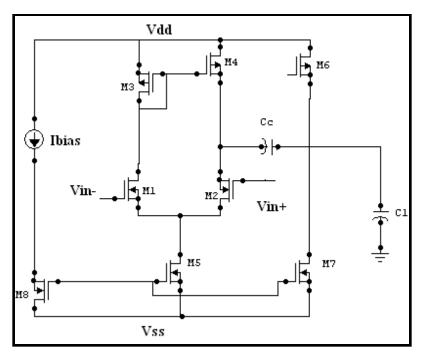

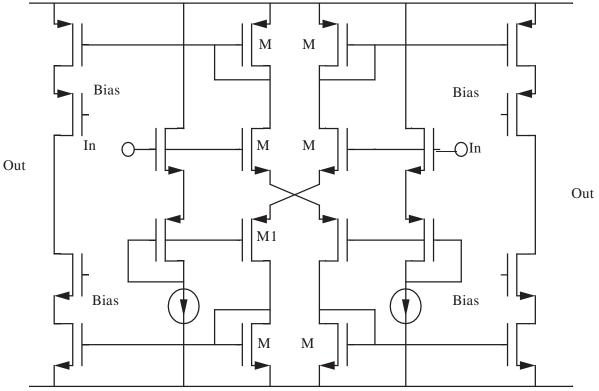

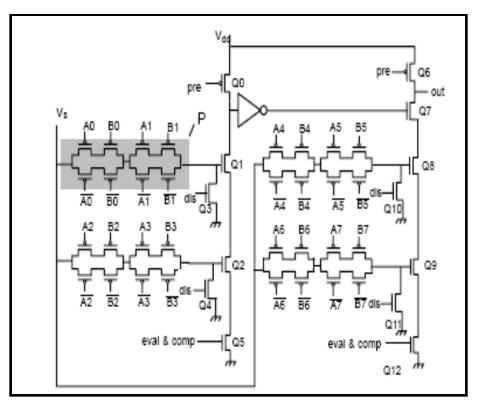

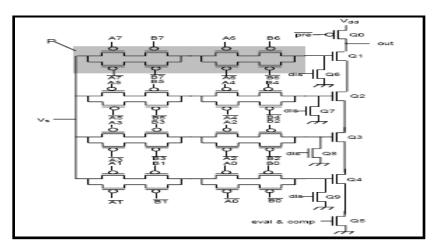

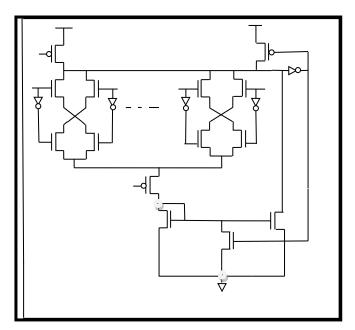

Figure 1.5(c): Two stage OTA consisting of eight transistors

The two-stage OTA circuit is appeared in fig 1.5 (c). This circuit includes eight standard semiconductors, with each semiconductor playing out a specific limit. Semiconductors M1 and M2 are the commitment for the essential stage (differential speaker), which changes over voltage signals into current. Semiconductors M3, M4, M5 and M8 go probably as a current mirror, while semiconductors M6 and M7 structure the second-stage intensifier. This geography has the upside of giving higher increase on the grounds that the subsequent stages give higher yield voltage swing. The inconvenience of this circuit is that it burns-through more force and gives negative force supply dismissal (PSR) at higher frequencies.

## 1.5.3 Telescopic cascode OTA

The Telescopic Cascode OTA setup is as demonstrated in figure while Single Stage OTA has low increase because of certainty that it has low impedance, at yield. Method of expanding one as the impedance is to add a few semiconductors at the yield including utilizing a functioning burden. Semiconductors are stacked on top of one another. The semiconductors are in this way called "Cascode", and will expand the yield of the impedance and consequently increment the increase Damera-Venkata et.al [28].

This design is known as a 'adjustable course operation amp' in light of the fact that the semiconductors are falls between the force supplies in arrangement and the semiconductor in the differential pair. This arrangement assembles the yield impedance and voltage procures on account of the course semiconductor and has low power usage. Its yield swing is little and it isn't

sensible for applications where the data and yield need to interface clearly, since this decreases its linearity range.

Figure 1.5(d): Telescopic OTA

Benefits

Higher speed it gives

Lower power utilization it has

Detriments

Additionally it has restricted yield swing.

It is troublesome shorting the info and yield is troublesome.

1.5.4 Regulated cascode (acquire boosting) OTA

In this sort of setup further addition of gain is additionally expanded without diminishing yield voltage swing likewise acquire is additionally expanded without adding more course gadgets. The Regulated Cascode OTA is appeared in figure

Figure 1.5(d): Regulated cascode OTA

The downside of this kind of arrangement is that these additional intensifiers may decrease by and large enhancer speed. Consequently, they ought to be planned in such a way to have a huge data transmission so as not to influence the transfer speed of the arrangement completely.

# 1.5.5 Folded cascode OTA

To eliminate the disadvantage of adaptive OTA all together that is limited yield swing and inconvenience in shorting the data and yield a Folded Cascode OTA is used. The figure of Folded Cascode OTA is showed up. The fell course OTA is showed up in Fig. 2. This circuit is called 'fallen course' since it folds down n-channel course unique piles of a differential pair and replaces the data semiconductor with a p-channel MOSFETs .The PMOS semiconductors M9 and M10 are used as differential data stages to charge the Wilson reflect (M5, M6, M7 and M8). The NMOS semiconductors M11 and M12 give the DC inclination voltages to semiconductors M5 through to M8. This topography improves the yield swing stood out from various geologies since it contains fewer semiconductors at the yield stage. Also, this topography has a predominant high-repeat power supply excusal extent (PSSR) and a more broad repeat response appeared differently in relation to the two-stage OTA. In any case, this geology consumes more power and adds to more conspicuous disturbance.

# Benefits

Comparing predominant plan has recurrence reaction than two-stage operational Amplifiers.

Additionally it has better high recurrence Power Supply Rejection Ratio (PSRR). The force utilization of this plan is approximately the equivalent similarly as that of the two-stage plan

#### Impediments

Disadvantages of Folded cascode has two extra current legs, and thusly for a given settling need which they will twofold the power dissipating. The collapsed course stage additionally has more gadgets which contribute huge info Referred warm commotion to that of sign.

Figure 1.5(e): Folded cascode OTA

Following figure sums up the examination of the diverse OTAs. Considering the table; the twostage OTA has higher increment differentiated and various geologies. This goes with lower speed stood out from various geologies. Among these three circuits, the imploded course has a higher speed differentiated and the others. In this work, as an element of a switch capacitor circuit for a capacitive sensor interface circuit, the two-stage OTA is picked on account of its high expansion, which is essential for this sort of utilization. In the accompanying portion, the arrangement of this two-stage OTA is discussed in detail.

#### 1.5.6 Direct Use of an OTA

Circuits for the OTA area are generally of a given application comprise of minor departure from a couple of fundamental sorts. These assortments are best seen by comparability to an ordinary semiconductor. In voltage mode when used the OTA territory can be worked in one of fundamental three states normal producer, regular base, and basic gatherer. In method of current the OTA can be utilized for calculation of simple like a speaker of current, a differentiator of current additionally a current integrator, and a gadget of current adding. This examines about the part and the utilization of an OTA in either the method of voltage or the method of current

For the increase in like manner E speaker arrangement is nearly set by eqn. 1 and the transconductance is nearly appeared in eqn. 2. Another term shows up in the condition, gm will be noted. Trans-conductance is that term of the OTA stage which might be best perceived as impedance with a yield of the E-terminal with estimation of 1/gm

$$G = R/(1/gm)/(+Re)$$

(1.5.1)

Gm deg =

$$1/(1/gm)/(+Rf)$$

(1.5.2)

#### **1.6 Types of operational trans-conductance amplifier**

Contingent upon the designs, of info and yield OTAs can be classified into three sorts:

Single information/yield operational trans-conductance intensifier

Differential-input single-yield operational trans-conductance intensifier

Differential information/yield (completely differential) operational trans-conductance speaker

In these three sorts of OTAs, the trans-conductance gm can be tuned through their DC current predisposition  $I_{tune}$ .

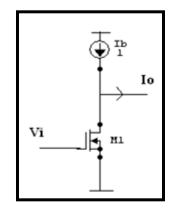

### 1.6.1 Single information/yield OTA

First sort of operational trans-conductance enhancer this is known dependent on its design of information/yield. It has single information and single yield hence the name is given single info/yield OTA. The image and its comparable circuit is appeared in figure

Figure 1.6(a): single input/ output OTA

Trans-conductor of the single info/yield appeared in Figure is the least complex to carry out, for example a solitary NMOS basic source trans-conductor. For high recurrence execution the effortlessness of this kind of OTA makes it intriguing. Li-pen Yuan at el. [16]

For this kind of OTA the yield current is given by,

$$IO = -gmVi \tag{1.6.1}$$

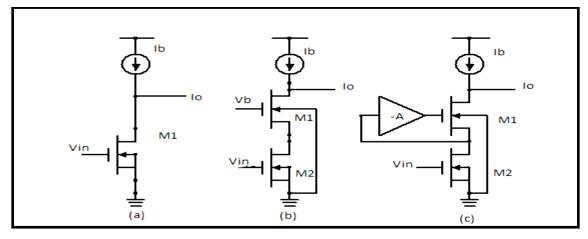

A portion of the basic geographies of CMOS are presents beneath to execute the OTAs single information/yield. The one in Figure (a) can't avoid being a lone NMOS customary source transconductor. Despite the way that it is the most un-troublesome and it has reasonably low yield impedance as a result of its Miller sway (input-yield coupling) and low linearity wandering it from an ideal OTA.

Figure 1.6(b): common source trans-conductor Single-input/output OTA

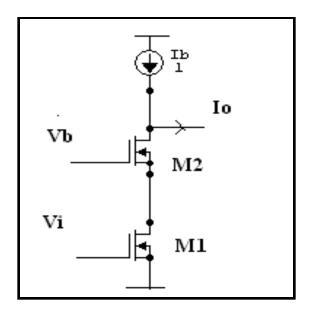

Issue, of this kind to lighten a cascode geography in Figure 1.6 is introduced, seclusion between the info and yield where a typical entryway semiconductor M2 is presented is given. This technique increments the yield impedance and linearity, yet additionally the transmission capacity and the accessible trans-conductance, higher voltage supply costs, with it

Figure 1.6(c): course trans-conductor with Single-input/yield OTA

As shown fig (c) the third kind of geography is shown varies from the course geography in its basic entryway semiconductor, where a PMOS semiconductor is applied rather than a NMOS one, bringing about a collapsed cas code geography. Same disconnection is given, however with a diminished voltage supply.

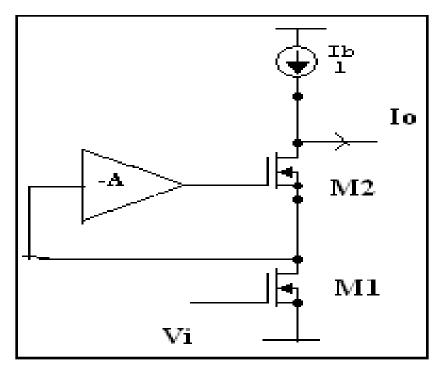

Figure 1.6(d): regulated -cascode trans-conductor with Single-input/output OTA

Figure shows about the directed cascode trans-conductor, which is an upgraded cascode transconductor. It replaces the door DC predisposition of M2 in Figure 1.6 with a negative input from its source. Where -An is the criticism acquire. This analysis further improves the linearity and the yield impedance by a factor of (A+1) diverged from the cascode trans-conductor.

Figure 1.6(e): regulated cascade trans-conductor with Single-input/output OTA

Figure 1.6 uses a current mirror PMOS to change a negative trans-conductor over to a positive one and for which the yield polarities of the square chart incorporating the circuit model in Figure must be upset to address it.

Figure 1.6(f): Single-input/output OTA with regulated cascade transconductor

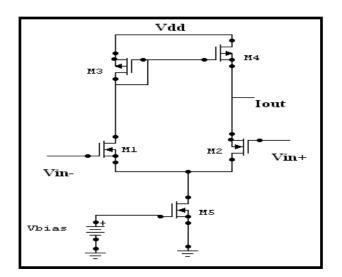

# 1.6.2 Differential-input/single - yield OTA

The second sort of operational trans-conductance speaker is of this kind and portrayed on its information/yield design further it has differential information and single yield consequently the name is given differential information single yield OTA alongside its image and its comparable circuit is appeared in fig.

Figure 1.6(g): Differential input single output OTA

Yield current is given by for differential info single yield OTA,

$$IO = gm(vi+-vi-)$$

(1.6.2)

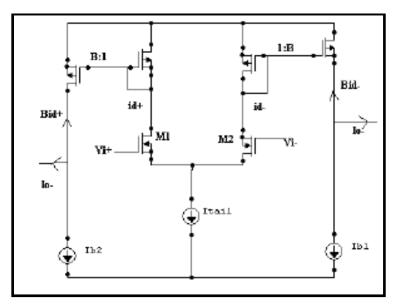

Figure1.6 shows two ordinary CMOS executions of the Differential info single yield OTA. This can give high information impedance, high expansion, and high ordinary mode excusal both of them contain a source-coupled differential-pair input stage, meanwhile missing a great deal of atonement.

Figure 1.6(h): differential-input single output simple CMOS OTA

In Figure 1.6(h) the current mirror CM moves the left yield current of the information differential pair, id + to one side to join with its correct yield current id— from which the trans-conductor yield current is multiplied accordingly Vi+ and vi— are the differential info voltages.

The execution of changed OTA isn't exactly equivalent to the one in Figure (a) in that two PMOS current mirrors are added after the data differential pair to improve the congruity between its two differential data ways.

# 1.6.3 Differential data/yield (totally differential) OTA

The third sort of operational trans-conductance speaker is of third sort reliant on its data/yield course of action also it has differential information differential yield subsequently the name is

given differential data differential yield OTA shown the picture and its indistinguishable circuit are showed up in figure 1.6.

Figure 1.6.3(i): Differential input differential output OTA

For differential information differential yield OTA, yield current is given by,

$$IO = IO + - IO = gm(vi + - vio)$$

(1.6.3)

The CMOS OTAs in Figure 1.6(j) and figure 1.6 (k) show two OTA executions for the differential information/yield OTA type.

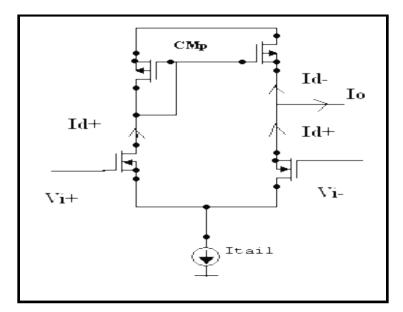

Figure 1.6(j): Differential input/output CMOS OTA

Figure 1.6(k): Differential input/output CMOS OTA

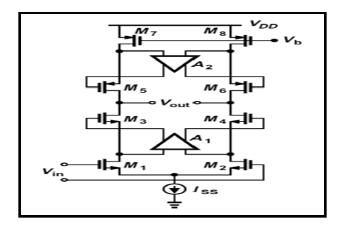

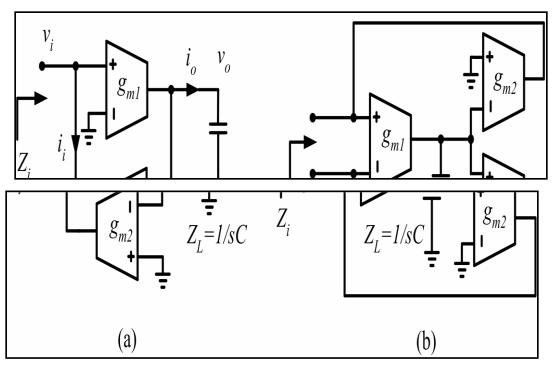

# 1.7 Proposed operational trans-conductance Amplifier (OTA)

A significant part of the main points of interest exist while picking an ideal plan for the operational trans-conductance enhancers. Both everywhere gain and huge transmission capacity exhibitions this decision pointed Burghartz J.N et al [29]. To achieve high expansion, the differential versatile geologies can be used. In this topography both the differential pair semiconductors and current mirror to grow load obstruction Yazdi.N et.al [30]. An operational trans-conductance intensifier (OTA) will be used as principal structure block in most of the traded capacitor channels OTA is basically an activity amp without a yield uphold and can simply drive capacitive weights. A trans-conductance is an enhancer where all centers are low impedance except for the yield and data centers. Trans-conductance can be changed by the inclination current an accommodating component of OTA.

By changing the tendency current Ibias channels made using the OTA can be tuned Masterminding an OTA for channel applications are the information signal abundance and the parasitic information/yield capacitances are two basic concerns. Planning an OTA for channel applications are the information signal adequacy and the parasitic information/yield capacitances are two significant concerns. OTA gain to become non-straight is huge signs cause moreover the external capacitance should be gigantic stood out from the data or yield parasitic of the OTA while this limits the most limit repeat of a channel worked with an OTA and causes or stage botches ampleness With suitable decision of Ibias these missteps can ordinarily be lessened as such the presentation of fundamental OTA is limited by its data and yield voltage swing. OTA and have an improved exhibition an OTA is utilized to conquer these restrictions of straightforward

## 1.7.1 Analog plan and Advancement

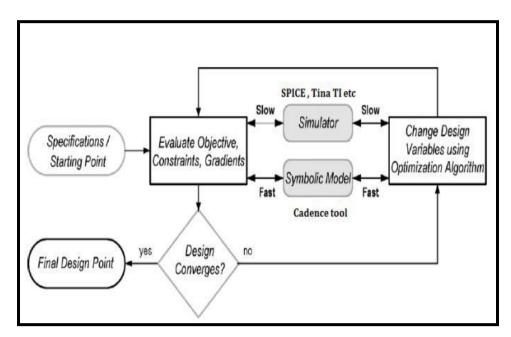

For huge circuits agent analyzers and, or test frameworks can be used to play out the robotized plan and improvement. The inclines and Hessian organizations can be found by two techniques Yoon.J at.el [33]. The improvement computation can disturb each factor and use the test framework to evaluate the objective and restrictions and thereafter register the slants and Hessians using restricted differences (a torpid cycle), or simply use the agent model to find the tendencies clearly by partition over the shut design enunciations of the objective and necessities (a fast communication).

Figure 1.7(a): Analog design automation and optimization

To a great extent, the analyzer can show up at an arrangement point that is reachable, yet restricted differences at the lead to an infeasible point which makes the enhancer isolated or stop carelessly. In such cases, giving slants and Hessians clearly from shut design enunciations allows the enhancer to converge to an answer. A typical arrangement upgrade circle is showed up in

Figure 1.7. The arrangement starts with a particular plan of subtleties and a beginning stage. Therefore the display estimations are surveyed at the current arrangement point Huang.C.H at.el [36]. This ought to be conceivable by getting back to the test framework, which is a particularly torpid communication. By using an absolute agent model in cadence gadget, which is speedier than the

Past, the smoothing out estimation by then changes the arrangement feature guarantee that the objective converges to the ideal and the goals are met.

We in this manner assume that discovering the point using restricted differentiations can be dreary, can provoke mixed up results, and may even explanation the enhancer to miss the mark. This can be especially interesting when the analyzer ought to be run on various events with new beginning point to find the globally ideal arrangement point Y. Wu at.el [40]. Each streamlining agent run itself includes different transient, commotion, and ac reenactments. This prompts ridiculously since quite a while past run times if a circuit test framework is used, regardless, for little and medium estimated circuits. All of these issues can be endure at whatever point shut design significant enunciations are free and are used for making the tendencies and Hessians. Such explanations speed up PC based improvements, and can on occasion give engineers setup in-sights and bargains, permitting them to make keen arrangement choices. Fashioners can use shut construction conditions to analyze a circuit and set up a fixed arrangement that can be used for the data based approach to manage basic arrangement computerization.

#### 1.7.2 Design and advancement of proposed OTA

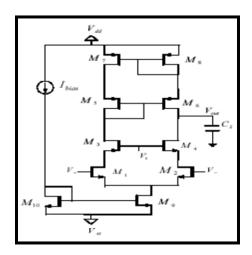

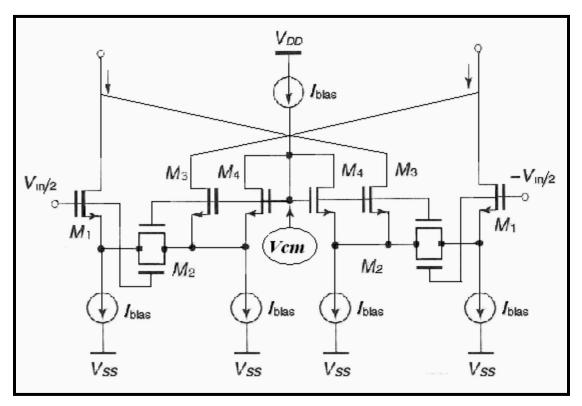

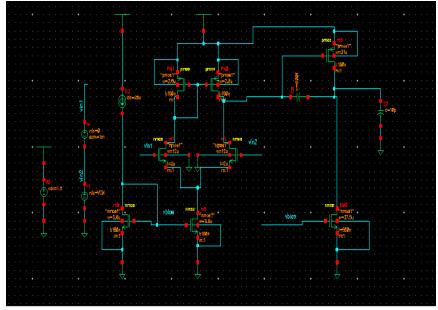

We portray the model utilized for the plan and enhancement two-stage OTA utilizing rhythm apparatus in this part, execution of the OTA with CMOS level is appeared in Figure.

Figure 1.7(b): Two phase CMOS Operational Trans-conductance Amplifier

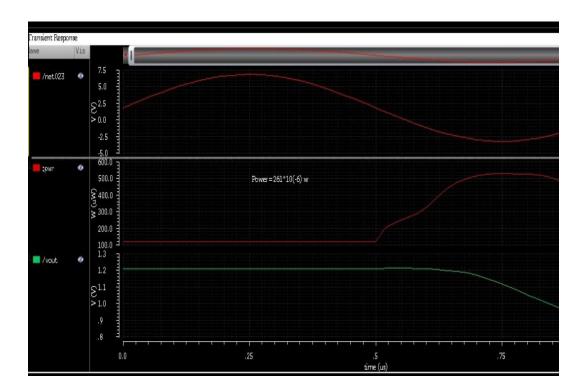

We start with a rundown of determinations summed up. These accepted qualities are for a normal 3 phase OTA phase of gain timed at 1Hz to 125 MHz which discovers applications in pipelined ADCs and SC delta-sigma modulators. The unique blunder detail of 0.1 suggests that the yield should settle to within $\pm$  0.1% of the at last the consistent state esteem inside 1.6 ns (1/2 clock cycle) when the inventory voltage is given as 1.2V.

## 1.7.3 Operation

CMOS M1: regular mode input voltage, the most minimal Vcm; min forces the hardest requirement on CMOS, m1 staying in immersion. CMOS M2: The precise counterbalance condition makes the channel voltage of m2 equivalent to the channel voltage of m2. Consequently, the condition for m2 being soaked is equivalent to the condition for m2 immersed right now. Note that the base sensible worth Vcm; min is directed by M1 and M2 entering the straight region. CMOS M3: Since Vgd3=0 CMOS M3: m3 is reliably in inundation and no additional basic is indispensable as such CMOS M4: The orderly counterbalanced condition likewise infers that the channel voltage of m4 is equivalent to the channel voltage at m3. Along these lines m4 also soaked. CMOS M5: The most critical normal mode input voltage, Vcm; max, powers the most secure necessity on CMOS m5 being in inundation the best appropriate

assessment of Vcm; min is directed by M5 entering the straight area anyway for CMOS M6: The most rigid condition happens when the yield voltage is at its base worth Vout; min. CMOS M7: For m7, the most serious condition happens when the yield voltage is at its most noteworthy worth V; max. CMOS M8: Since Vgd8=0, CMOS M8 is reliably in submersion. The increased yield (Vout) on the last stages

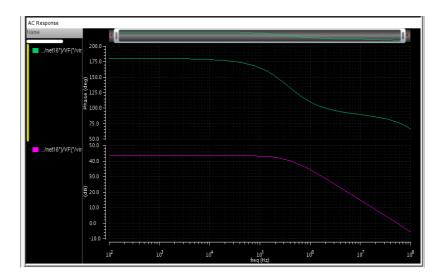

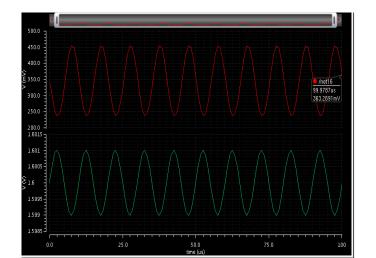

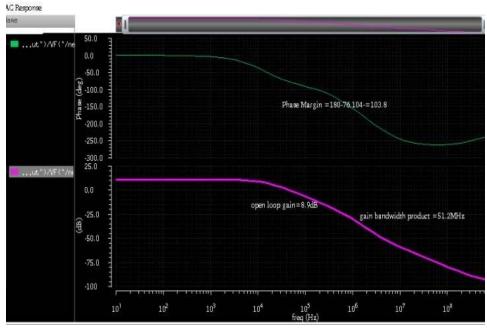

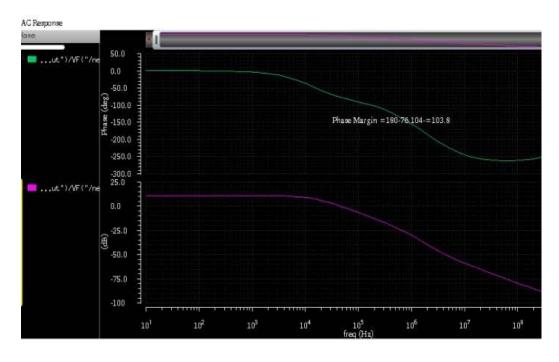

Since the AC repeat response is a huge factor for any intensifier which helps with determining the information move limit and the increment. The AC recurrence reaction is staying consistent up to the 10MHz and the most extreme voltage on the recurrence reaction is about 5.03mV. By working all CMOS in to submersion region power usage and slew rate is diminished anyway GBW thing stays consistent. Repeat response reenactment of yield repeat is showed up in figure 5. If the OTA is moved toward the some nanometer level the characteristic expansion has been extended 30 and nearby 50 independently. In this philosophy the OTA is arranged in the level of 90nm on musicality instrument.

#### 1.7.4 Characterization

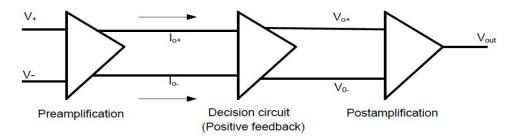

Improving the settling execution by Phase-edge changes has been proposed in the composition. In any case, for two-stage speakers, better stage edge doesn't by and large recommend speedier settling. Voltage controlled current source is an OTA even more unequivocally the term operational comes from the way that it takes the differentiation of two voltages as the commitment for the current change.

#### 1.7.4.1 Gain and phase margin

The utilization of negative information requires examination of the open circle procure. A couple of circuits will cause a stage move in the information signal enormous enough that the criticism gets positive (adds to the information), bringing about a temperamental framework. Steadiness requires a stage move in the criticism signal under 180° for open circle acquire values bigger than 0 dB. Requires like this is the prerequisite of definition for two proportions of solidness of the addition edge (GM) and furthermore of stage edge (PM) boundaries of gain including stage edge can be estimated at the investigation of the open circle recreation of AC reaction and gain edge is characterized as the distinction (in dB) in the increase at a period of - 180° and acquire including solidarity Xiao.H at el [43]. Plan rules regularly determine a GM more prominent than

10 dB. The stage edge is characterized as the distinction (in degrees) in the stage at solidarity acquire and - 180°. The stage edge ought to be

More noteworthy than 45° with an ideal, fundamentally damped, estimation of 60° for PM esteems under 60° the under damped framework and the qualities are appeared of transient reaction will demonstrate expanded slew rate. For PM esteems more noteworthy than 60° overdamped of the framework, and the reproduced rules of transient reaction will demonstrate diminished slew rate. Stage edge depends upon the overall circumstance of the extraordinary repeat shaft fPA and the expansion information transmission (fortitude gain repeat). The circumstance of the extraordinary repeat shaft territory is in this manner directly related to the stage edge.

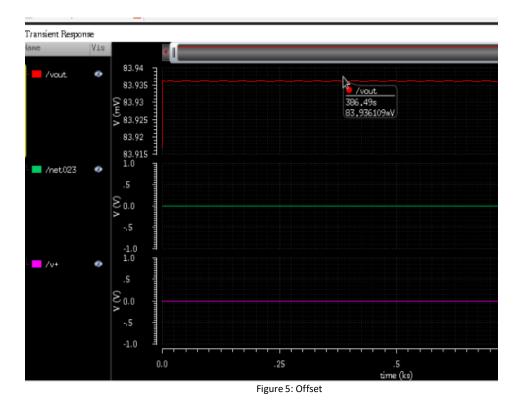

## 1.7.4.2 Input balance voltage

Ideally, if the two commitments of the OTA are grounded, the yield voltage should be zero. In every practical sense, a nonzero yield voltage (balance) will be accessible and is a direct result of unpredictable and exact bungles Zhang.J et.al [47].

#### 1.7.4.2.1 Random counterbalance

Irregular blunders are because of bungles in the info stage because of manufacture including (yet not restricted to) edge voltage contrasts and mathematical contrasts. Irregular mistakes can be assessed through Monte Carlo reenactments.

## 1.7.4.2.2 Systematic balance

Deliberate goofs are intrinsic to the arrangement. Efficient bumbles can be the result of nonbalances in the OTA design, making voltage and current perplexes. The effective offset can be settled through entertainment and will be evident in the DC clear reenactment as the equilibrium from the zero-zero square where the data voltage and yield voltage should both identical zero.

# 1.7.4.2.3 Total consonant twisting

Preferably, the yield of an intensifier is a copy of the information signal scaled by the development A. The development for giant sign data sources is needy upon the information signal plenty fullness. For a totally sinusoidal data signal:

$$V_{in}(t) = VM \sin(wt)$$

(1.7.4.2.3.1)

The non-ideal caution sign of an enhancer can be imparted as:

$$V_{OUT}(t) = a1VM(\omega t) + a2VM \sin(2\omega t) + \dots + anVM \sin(n\omega t)$$

(1.7.2.3.2.2)

Where the ideal yield is an essential a1VM sin ( $\omega$ t) and preferably a2 through a zero

#### 1.7.5 Noise sources in OTA

Prepared by coordinated circuits as the simple signs are tainted by commotion of various kinds electronic gadgets clamor and "ecological clamor", cutoff points of commotion the base sign level adequate quality that a circuit can measure with. Since it exchanges with power dissemination, speed and linearity, the present simple architects continually manage the issue of clamor. Doing proficient plan necessitates that clamor be taken promptly in to a record likewise the other circuit boundary like addition and info/yield impedance including numerous others Next we talk about the commotion sources in a MOSFET and think about strategies for addressing commotion in circuits.

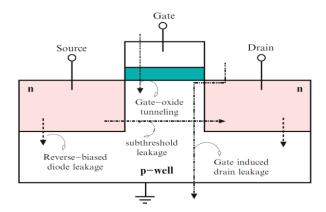

## 1.7.5.1 MOSFET Thermal commotion

Source which is the most critical the clamor produced in the channel. The irregular movement of electrons is warm in the channel which is equipped for presenting variances in the voltage estimated across the channel regardless of whether the zero is the normal current of its capacity. As such we can say about the warm noise of reach is comparative with by and large temperature T also value of dependence of uproar of warm upon temperature suggests that low temperature movement can reduce the upheaval in basic circuits. The warm clamor can be displayed by a wellspring of current which is additionally associated between the channel and source terminals as demonstrated in Figure 1.7 with ghastly thickness given by Pozar.D.M, at el.[19]

$$IN2 = 4kT\gamma gM \tag{1.7.5.1}$$

Where Boltzmann's steady is K and supreme temperature is T in Kelvin, gm is the gadget transconductance consistent is  $\gamma$  [5] taken to be 2/3 for above edge and 1/2 for beneath edge conduction for long channel semiconductors. Their incentive for short channel semiconductors is as yet a subject of examination

## 1.7.5.2 Flicker commotion

Gleam commotion is available under DC conditions and is the consequence of electron catching (deferred discharge) because of silicon blemishes in the semiconductor. Contrarily proportionality of glimmer commotion is to recurrence and is by and large alluded to as 1/f clamor. The accompanying type of commotion can be displayed with as wellspring of current and furthermore with the semiconductor in equal way

KF is a cycle subordinate glimmer upheaval predictable with construed assessment of 10-25 V2 F. AF is a consistent with its value lying some place in the scope of 0.5 and 2, ID is the channel current (DC), Cox is the capacitance per unit zone, gm is the contraption trans-conductance and f is the repeat

Uproar sources are given as far as per unit information transmission. There can be a fascinating chance of lower recurrence cut-off flash clamor being zero. As the gleam clamor has a logarithmic reliance on recurrence this yields a boundless incentive for complete commotion. Also in the event that we notice the circuit for seemingly forever, the exceptionally lethargic commotion segments can haphazardly accept an enormous force level. At such torpid rates, commotion gets vague from warm buoy or developing of devices. This prompts the going with closes: first since the signs experienced in quite a while don't contain colossal low recurrent segments, our insight window need not be incredibly long. Besides, the logarithmic reliance of flash commotion over f1 permits some wiggle room in choosing f1. To evaluate the meaning of 1/f clamor concerning warm commotion for a given gadget, we plot both phantom densities on similar tomahawks and decide their convergence point. Called the "corner recurrence", the convergence point acts as a fundamental estimation of which piece of the band to be utilized is for the most part undermined by glint clamor.

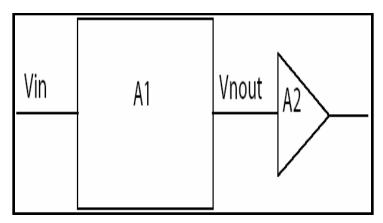

1.7.5.3 Representation of clamor in circuits

The normal way to deal with evaluate the impact of commotion in a circuit is to add up to clamor estimation at the yield because of the numerous different wellsprings of commotion in that of circuit. While naturally engaging, the yield alluded commotion doesn't give a helpful examination of the presentation of various circuits since it relies upon the increase. Consider a framework with commotion at the yield equivalent to Vnout2 followed by an enhancer at the yield phase of gain A2 as effectively depicted in figure including the all out yield clamor is equivalent to the Vnout2 increased by A2. Considering just the yield clamor we may reason that if the addition A2 expands, the circuit becomes noisier which is an inaccurate outcome in light of the fact that a bigger A2 likewise gives a relatively higher sign level at the yield. That is the caution sign to upheaval extent doesn't depend upon A2.

Figure 1.7(c): Additional gain stage at the yield

To crush this scratch we show the "input-insinuated upheaval" of the circuits. The contemplation is to address the effect of upheaval sources in the circuit by a single source Vn, in2 at the data so much that the uproar on the limit of yield is comparable to the yield disturbances if all the uproar sources in the circuit were to be considered autonomously. Av is the voltage acquire then activity should have Vn,out = AVn,in 2, alluded to as the info commotion in the straightforward case is the yield clamor voltage isolated by the addition.

# **1.8 Comparisons of Different Configurations**

Exchange's superior operation amps offer rail-to-rail inputs/yields and a wide working voltage (1.7 V to 5.5 V) to intensify battery life, decline dynamic arrive at issues, and cutoff design issues.

Talk miniature force activity amps pair agreeably with our overly low power Green PAK Mixedsignal Matrix things

1.8.1 Applications

• Portable things with battery gauges under 400mAH requiring a straightforward front completion to connect with various sensors

- Bio-metric identifying wearable's

- Consumer check scales

- Long term distinguishing clinical devices for most normal signs

- Isolated power clinical circuits

• Remote metering, for instance, water meters, gas meters, or even power meters that should work for a broad time frame with the power unattached

- Ambient light sensors

- Remote security devices and sensor center points

- Industrial sensors that are power isolated or related simply through their correspondence transport

- Energy gathering energized things

1.8.2 Methods of Operation

Needed in battery worked framework (pocket adding machines, pace producers, portable hearing assistants, electronic phone,) Utilization < 1  $\mu$ A Utilization of MOS semiconductors in frail reversal (sub edge) Low current has, as outcome, low slew rate.

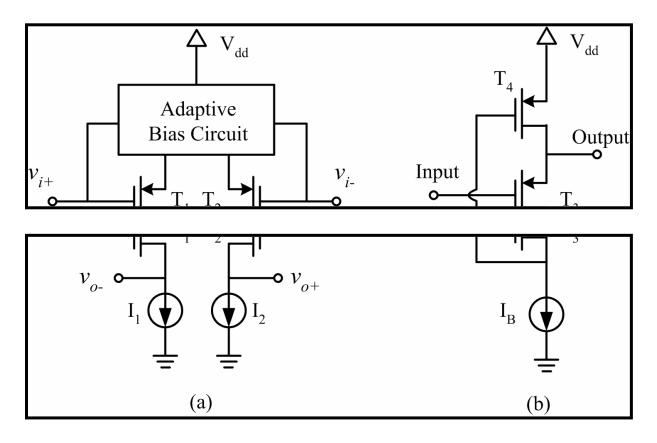

Figure 1.8(a): Amplifier with adaptivebiases

# 1.8.3 Amplifier with adaptive biases Produce |I1 - I2| and increment the current in the differential stage by D|I1 - I2|.

Ordinary exhibitions

DC gain 95 dB

ft 130 kHz

SR  $0.1 \text{ V/}\mu \text{ sec}$

ΙΟ 0.5 μΑ

Itot 2.5 µA

1.8.4 Class AB Single stage with Dynamic Biasing

Figure 1.8 (b): Class AB Single stage with Dynamic Biasing

To have a greatest yield swing the inclination voltages BIAS1 - BIAS2 should be kept as close as conceivable to the predisposition voltages

During the slewing the current wellspring of the yield cascodes can be pushed in the immediate area, from this time forward losing the potential gain of the AB movement.

The issue is addressed with the dynamic biasing

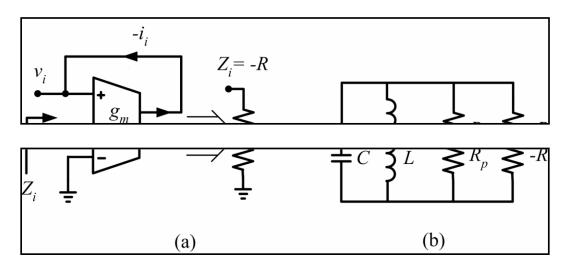

# 1.8.5 Noise

The upheaval of an operational enhancer is depicted with an information suggested voltage source Vn.

The scope of Vn is made of a white term and 1/f term.

Falling speakers is generally a fair strategy to achieve the ideal open circle procure regardless; strength and settling speed become a concern

# 1.8.6 High addition intensifier engineering

High expansion intensifiers with speedy settling times are needed for quick data converter applications. Falling speakers is for the most part a good methodology to accomplish the ideal open circle get in any case; strength and settling speed become a worry. A falling designing that is normally consistent and keeps up incredible settling execution

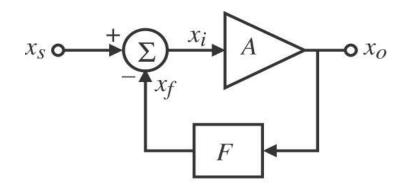

$$A = X/V A/(1+AF) \sim 1/F$$

(1.8.6.1)

Where x is Voltage/Current

Figure 1.9 Model of High Gain Architecture

# **1.9 Examinations of various arrangements**

The correlation of fundamental operation amps boundary addresses in table for various setup is depicted.

| GAIN | OUTPUT<br>SWING | SPEED | POWER | NOISE |

|------|-----------------|-------|-------|-------|

|------|-----------------|-------|-------|-------|

| TELESCOPIC<br>CASCODE | MEDIUM | MEDIUM  | HIGHEST | LOW     | LOW    |

|-----------------------|--------|---------|---------|---------|--------|

| FOLDED CASCODE        | MEDIUM | MEDIUM  | HIGH    | MEDIUM  | MEDIUM |

| TWO STAGE             | HIGH   | HIGHEST | LOW     | MEDIUM  | LOW    |

| REGULATED<br>CASCODE  | HIGH   | MEDIUM  | HIGHEST | HIGHEST | MEDIUM |

Table 1.9: various op-amp parameter comparison

As depicted in Table 1.9, with the end goal of plan the adaptive and multi stage geographies saw to be more appropriate for the planning reason. It will encounter the evil impacts of low yield swing and medium expansion regardless of meeting the hand create points of interest yet if unadulterated versatile, Lin.R, et al. [21]. Regardless for the multi stage geography more than the two phases issue of security seriously become for us. Two totally differential aide operational speakers act like a support in solicitation to get an adequately high expansion, Fernàndez et al. [22]. Here we will depict the two stage geology procedure for the enhancer plan in this proposition.

|       | Topology       | Gain     | Output<br>Swing | Speed   | Power    |

|-------|----------------|----------|-----------------|---------|----------|

|       | Two-stage      | High     | Highest         | Low     | Medium   |

|       | Telescopic     | Medium   | Medium          | Highest | Low      |

|       | Folded cascade | Medium   | Medium          | High    | Highest  |

| Fable | Tonee cuscule  | Weddulli | Weddulli        | mgn     | ingliest |

Comparison of various geographies

1.9:

| Specifications                        | Value  |

|---------------------------------------|--------|

| Differential gain, Av (dB)            | ≥70    |

| Gain bandwidth product , GBW<br>(MHz) | ≥20KHz |

| Phase margin, PM (degree)             | ≥60    |

| Slew Rate, SR (V/µs)                  | ≥40    |

| Average Power consumed, P(mW)         | <5     |

| Force source, Vdd (V)                 | 2.5    |

| Yield load capacitance, CL (pF)       | 3      |

| Compensation Capacitance, Cc (pF)     | 1.1    |

| Input offset voltage, Vos (V)         | 10mV   |

|                                       |        |

Table 1.10: OTA Specification

# **1.10 Examination procedure**

The OTA is a fundamental square of working in various basic circuits which are found including data converter's (ADC &DAC) and moreover fuses Gm-C channels. Gm-C channels execution is related to OTA execution. Trans-conductance intensifier OTA is an info voltage control gadget which is constrained by the yield current. Additionally it implies that voltage control current source is an OTA while voltage controlled voltage source are OTA. Essentially an OTA is without support yield so it can just load drive. Portrayal of this theory is finished with various sorts of CMOS OTA with its essential thing. Additionally depicted CMOS OTA the diverse geography and finally there is a correlation between setups of various sorts of OTA are given. In this part, the plan of the two-stage OTA, as demonstrated in Fig. 1, is talked about. The hidden detail of the arrangement is set as exhibited in Table II. We use the gm/Id system to choose the

semiconductor estimating (W/L) for each semiconductor in the OTA circuit. The arrangement started by evaluating the assessment of the compensation capacitor, Cc. For a 600 stage edge, the going with condition is used:

$$Cc = 0.22 \times CL \Longrightarrow Cc = 3pF \tag{1.10}$$

Then, the inclination current, Ibias, was resolved dependent on the huge number rate detail.

$I_{\text{bias}} = 80 \ \mu\text{A}$  was evaluated as given by the going with condition:

At the point when Vgd3 = 0, the semiconductor M3 is in an immersion district. As the precise balance condition gives that the channel voltage of M4 is equivalent to the channel voltage of M3. M2 and M1 have same worth. At that point, the semiconductor assessing for M8 is settled from Vgd8 = 0, where it works in an inundation region. The size of semiconductors M5 and M6 will be resolved next using the current mirror thought with semiconductor M8. In this arrangement, the semiconductor length is set to  $L = 1 \mu m$ . Taking into account the above discussion, W1 = W2, W3 = W4 and W5 = W8. Along these lines, I1, I5 and I7 can be conveyed by conditions (3) to (5). In this plan, we utilized a course current mirror (M9-M13) as a biasing circuit for M8.

| Devices                | Value    |     |  |

|------------------------|----------|-----|--|

|                        | W        | L   |  |

| M1,M2                  | 10µm     | lµm |  |

| M3,M4                  | 20µm     | lµm |  |

| M6                     | 200µm    | 1µm |  |

| M7                     | 100µm    | lµm |  |

| M8,M5                  | 40µm     | 1µm |  |

| M9,M10,M11,M12,M13     | 25µm     | 1µm |  |

| Supply voltage         | Vdd=2.5V |     |  |

| Load Capacitance (CL)  | 3pF      |     |  |

| Compensation Capacitor | lpF      |     |  |

| Bias current, Ibias    | 70μΑ     |     |  |

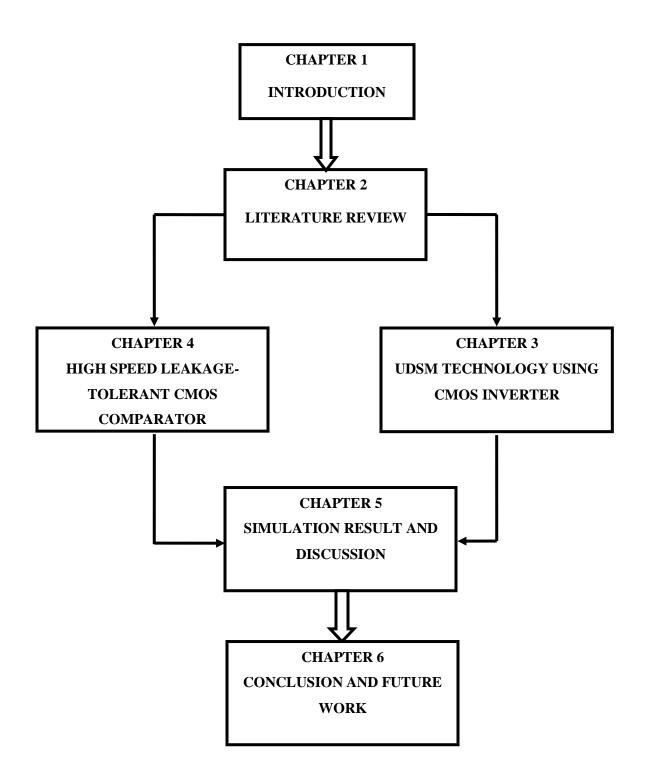

## 1.11 Organization of the thesis

The proposition is separated in to seven primary parts as we can say sections and portrayed with its framework given beneath.

## **Section 1: Introduction**

Outline brief issues identified with present day CMOS innovation, inspiration of venture and need of recurrence remuneration and sorts of OTA utilized with proposed OTA plan engineering and incorporates theory diagram.

## **Section 2: Literature Review**

Operational trans-conductance enhancer begins with the section outlines and clarifying about the various strategies likewise there is essentially depicted about early history of OTA including patterns and different boundaries utilized. We depict the OTA circuit and the different portrayal boundaries. We present the commotion sources and talk about their portrayal in a circuit.

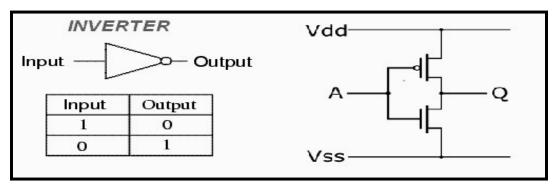

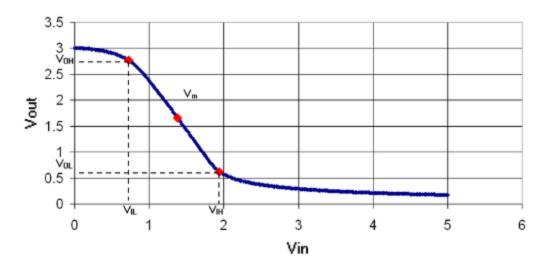

## Section 3: UDSM Technology utilizing CMOS Inverter

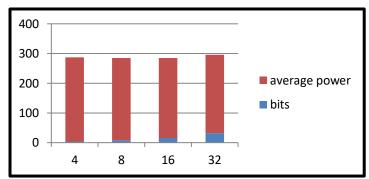

In this paper we stress the practically identical assessment of deferral, customary force and spillage force of CMOS inverter in Ultra Deep Submicron Technology range. This assessment shows assortment of following as follows by deferral to UDSM development and besides for ordinary power and spillage power by lessening to certain advancement. CMOS development had achieved pivotal to progress and advances in like manner this headway had been cultivated by certain scaling back of the MOSFETs. The component of the MOSFETs were scaled upon by factor which has undeniably found to be 0.7 in colossal degree blend advancement, drive and delay assessment have become critical arrangement concern. The reenactment results are taken for 45nm in Ultra Deep Submicron Technology range with the help of Cadence Tool and besides analyzing the effect of weight capacitance, semiconductor width and supply voltage on typical power and delay of CMOS inverter of 45nm advancement thusly Neil H.E.at.el [52]. Therefore the examination has gotten done with the plan to see about the particular assortment in deferral

and power with assortment in semiconductor width in UDSM CMOS inverter and moreover had assortment in load capacitance and supply voltage had been inspected.

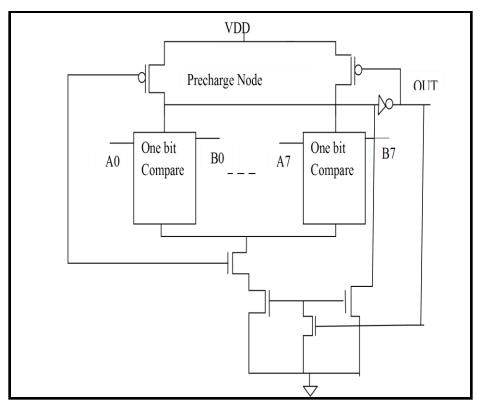

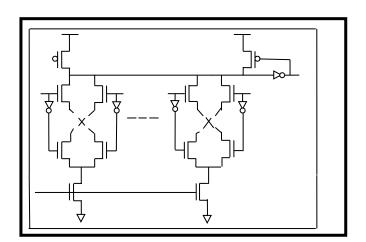

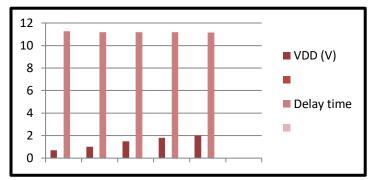

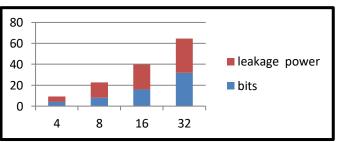

# Section 4: High Speed Leakage Tolerant CMOS Comparator

This part stresses a proposed comparator configuration circuit which devours low spillage power and had a higher speed than different circuits. The deferral, spillage power and ordinary power of the proposed CMOS Comparator circuit have been resolved and reproduced for different pieces. The outcome shows a little region overhead and around 10-30% decrease in all out power dispersal happened.

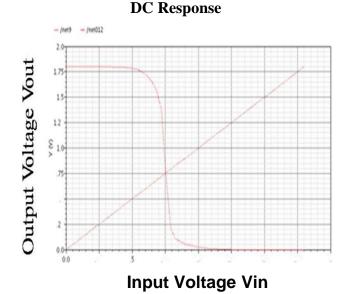

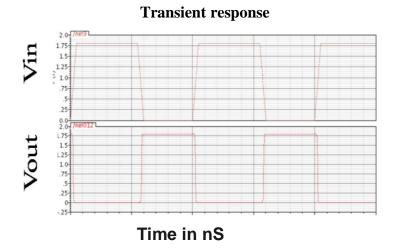

# **Section 5: Simulation Work**

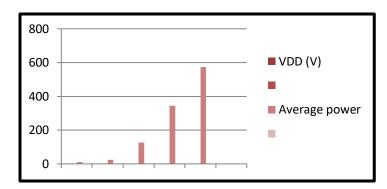

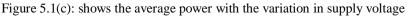

This section contains different recreation aftereffect of the last circuit; we have proposed a 2 phase CMOS OTA and broke down its conduct Lopez-Martin at el [54]. Propagation results certify that the proposed plan technique can be utilized to design activity amps that meet all of the fundamental subtleties. Plan methods for this operation amp were additionally given. The proposed system is generally precise.

# Section 6: Conclusion, Future work and List of distribution

This part which is the finishing up section, the plan has been broke down for additional enhancements which are conceivable, likewise been portrayed Work to be done: we notice that limit is most extreme in the event that we work the speaker at a lot higher frequencies. In any case, these intensifiers are intended for applications at low recurrence. Is it practical to move the ghostly substance of the sign to these higher frequencies without burning through more effort simultaneously? Is it conceivable to move the data transmission of the framework to a higher recurrence to amplify limit however keep the ideal recurrence selectivity of the framework? These are a portion of the issues that will be managed later on.

# **CHAPTER 2**

# LITERATURE REVIEW